대세는 미세공정…EUV 확보 사활 [반도체 불황 극복 기술에 답 있다 ②]

성능·효율 개선에 생산량 증대 효과까지

대당 2천억 넘는 EUV “없어서 못 판다”

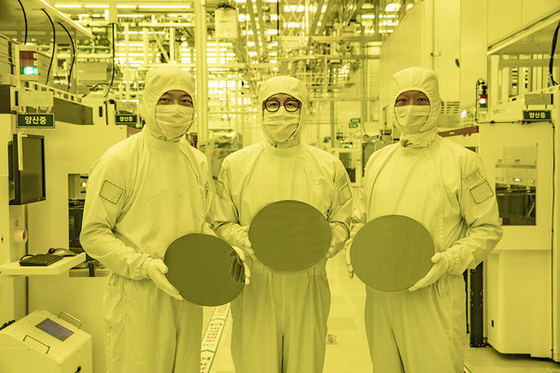

1일 반도체 업계에 따르면 삼성전자와 SK하이닉스는 미세공정이 적용된 라인에서 시스템 반도체와 D램 등 주력 제품을 생산하고 있다. 양사 모두 글로벌 반도체 시장을 선도하고 있는 만큼 경쟁 업체와의 격차를 벌리기 위해 미세공정을 적극적으로 도입하고 있는 것이다.

미세공정 도입을 통해 얻을 수 있는 효과는 상당하다. 우선 반도체에 세기는 회로가 더욱 얇아지는 만큼 생산 효율이 올라간다. 공정이 미세할수록 다이(Die, 회로가 새겨지는 작은 사각형 조각) 크기를 줄일 수 있는 만큼 한 웨이퍼로 더 많은 반도체 칩을 생산할 수 있다.

또 같은 다이 안에 세밀한 회로를 새길 수 있기 때문에 반도체 성능과 직결되는 트랜지스터를 더 많이 넣을 수 있다. 여기에 트랜지스터의 밀집도가 높은 만큼 전력 효율도 상당 부분 개선된다. 즉 미세공정이 적용됐다는 뜻은 기존보다 성능과 효율을 개선하면서 더욱 많은 반도체 칩을 생산할 수 있다는 뜻이다.

삼성·SK 기술 초격차 속도

실제 삼성전자는 올해 상반기 세계 최초로 3나노 파운드리 양산에 성공하며 경쟁사 대비 한 발 더 앞서 나가게 됐다. 특히 삼성전자는 3나노 공정에 차세대 GAA 기술을 세계 최초로 적용했다. GAA 기술은 반도체를 구성하는 트랜지스터에 전류가 흐르는 채널(Channel) 4개면을 게이트(Gate)가 둘러싸는 형태로 이뤄져 있다. 이는 TSMC가 준비 중인 핀펫(FinFET) 방식 대비 데이터처리 속도가 빠르다는 이점이 있다.

또 지난해 10월에는 EUV 공정을 적용한 업계 최선단 14나노 D램 양산에 들어갔다. 이를 통해 삼성전자는 D램의 성능과 수율을 향상시키고 14나노 이하 D램 미세 공정 경쟁에서 확고한 우위를 확보해 나갈 계획이다. 삼성전자 14나노 D램은 업계 최고의 웨이퍼 집적도로 이전 세대 대비 생산성이 약 20% 향상된 것으로 알려졌다.

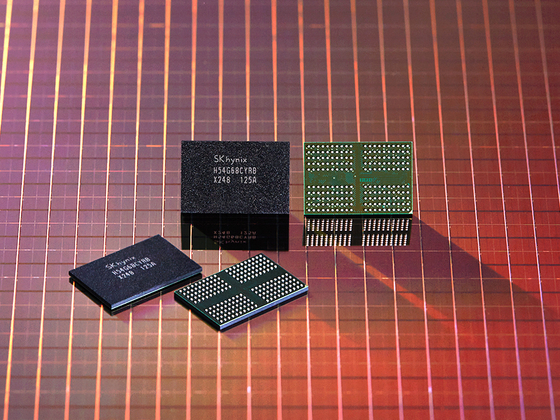

SK하이닉스는 지난해 7월 10나노급 4세대(1a) 미세공정을 적용한 8기가비트(Gbit) LPDDR4 모바일 D램 양산을 시작했다. 반도체 업계는 10나노대 D램부터 세대별로 알파벳 기호를 붙여 호칭하고 있으며, 1x(1세대), 1y(2세대), 1z(3세대)에 이어 1a는 4세대 기술이다. 1a 기술이 적용된 모바일 D램은 지난해 하반기부터 스마트폰 제조사들에게 공급되고 있다.

해당 제품은 SK하이닉스의 D램 중 처음으로 EUV 공정 기술을 통해 양산된다는 의미가 있다. SK하이닉스는 이번에 EUV 공정기술의 안정성을 확보한 만큼, 향후 1a D램 모든 제품을 EUV를 활용해 생산한다는 계획이다. 앞서 SK하이닉스는 1y(2세대) 제품 생산 과정에서 EUV를 일부 도입해 안정성을 확인한 바 있다.

SK하이닉스 관계자는 “EUV를 양산에 본격 적용함으로써 최첨단 기술을 선도하는 기업으로서의 위상을 공고히 할 수 있을 것”이라고 설명했다.

EUV 확보가 곧 경쟁력

네덜란드 ASML이 독점 생산하고 있는 EUV 노광장비는 반도체 웨이퍼 원판에 빛을 쪼여 회로 패턴을 그리는 포토(노광)공정에서 활용되는데 극자외선 파장의 광원을 사용한다. 기존 액침불화아르곤(ArF)의 광원보다 파장의 길이가 짧아(10분의 1 미만) 반도체에 미세 회로 패턴을 구현하는 데 유리하고 성능과 생산성도 높일 수 있다는 장점이 있다. 이 때문에 EUV 노광장비는 반도체 선폭이 7나노 이하의 선단(첨단) 공정 가동을 위해서는 반드시 필요한 장비다.

대당 가격이 2000억원이 넘지만 미세공정 구현을 위해 수요는 여전히 높다. 앞서 3나노 도입 과정에서도 삼성전자와 TSMC는 ASML의 노광장비를 선제적으로 확보하기 위해 물밑경쟁을 펼친 바 있다. 최근에는 차세대 EUV로 불리는 ‘하이(High) NA’를 ASML 고객사 모두가 발주한 것으로 알려지며 눈길을 끌었다. 하이 NA는 기존 EUV 대비 미세한 반도체 회로를 그릴 수 있어 차세대 공정인 2나노미터(nm,1nm는10억분의1m) 실현을 위한 필수 조건으로 여겨지고 있다.

한 업계 관계자는 “반도체 수요가 줄어들고 업황이 안 좋아질수록 기술 초격차를 통한 차별화가 무엇보다 중요하다”며 “이러한 관점에서 미세공정 경쟁은 전 반도체 분야에서 더욱 치열해질 수밖에 없고 EUV 확보전 또한 뜨거워질 것으로 보인다”고 설명했다.

이건엄 기자 Leeku@edaily.co.kr

ⓒ이코노미스트(https://economist.co.kr) '내일을 위한 경제뉴스 이코노미스트' 무단 전재 및 재배포 금지

많이 본 뉴스

1서학 개미에게 희소식…하루 23시간 거래 가능한 미 증권거래소 내년 개장

2 오세훈 시장 "동덕여대 폭력·기물파손, 법적으로 손괴죄…원인제공 한 분들이 책임져야”

3미·중 갈등 고조되나…대만에 F-16 부품 판매 승인한 미국의 속내는

4"나도 피해자” 호소…유흥업소 실장, 이선균 협박으로 檢 징역 7년 구형

5배우 김사희 품절녀 된다...두살 연상 사업가와 결혼

6정기선 HD현대 부회장의 바이오 진출 이어진다…신약개발 자회사 ‘에이엠시사이언스’ 설립

7공동 사냥한 게임 아이템 ‘먹튀’ 소용없다…”게임사가 압수해도 정당” 판결 나와

887억 바나나 '꿀꺽'한 코인 사업가..."훨씬 맛있다"

9AI 학습 데이터의 저작권 소송 이어져…캐나다 언론사 오픈AI 상대로 소송